RISC (Reduced Instruction Set Computing) simplifies processor design by using a smaller set of instructions, enabling faster execution and greater efficiency in embedded pet technology devices. CISC (Complex Instruction Set Computing) contains more complex instructions, allowing more functionality per instruction but often at the cost of speed and increased power consumption. For pet technology, RISC processors typically offer better performance and lower energy usage, which is crucial for portable and battery-operated pet gadgets.

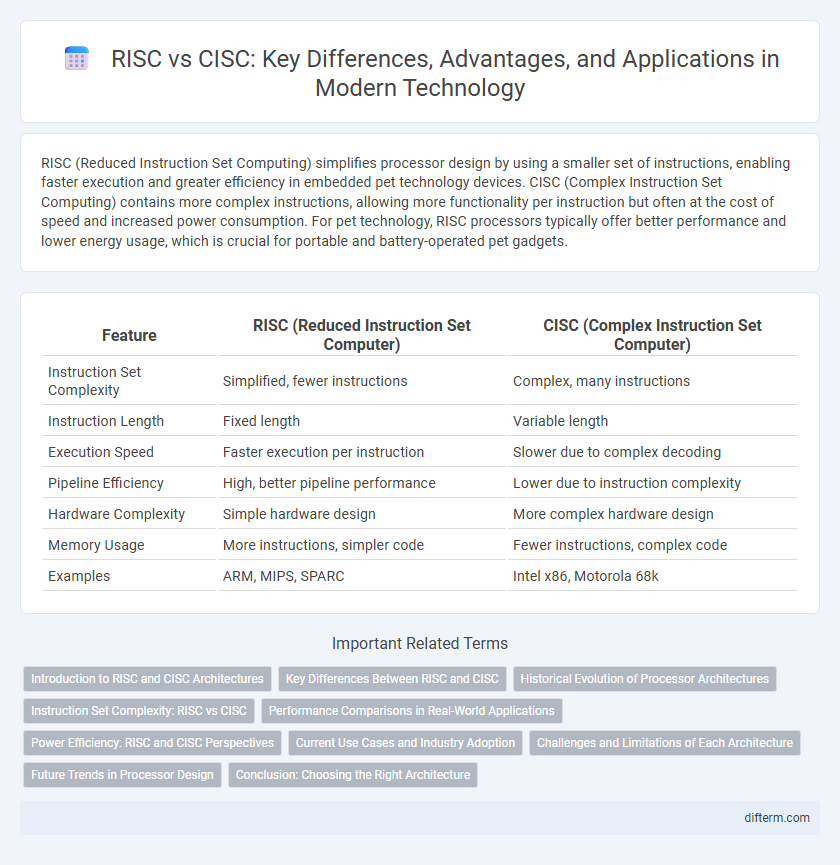

Table of Comparison

| Feature | RISC (Reduced Instruction Set Computer) | CISC (Complex Instruction Set Computer) |

|---|---|---|

| Instruction Set Complexity | Simplified, fewer instructions | Complex, many instructions |

| Instruction Length | Fixed length | Variable length |

| Execution Speed | Faster execution per instruction | Slower due to complex decoding |

| Pipeline Efficiency | High, better pipeline performance | Lower due to instruction complexity |

| Hardware Complexity | Simple hardware design | More complex hardware design |

| Memory Usage | More instructions, simpler code | Fewer instructions, complex code |

| Examples | ARM, MIPS, SPARC | Intel x86, Motorola 68k |

Introduction to RISC and CISC Architectures

RISC (Reduced Instruction Set Computer) architecture emphasizes a small, highly optimized set of instructions for faster execution and simpler hardware design, improving performance and power efficiency. CISC (Complex Instruction Set Computer) architecture features a broad set of instructions aiming to complete tasks with fewer lines of assembly code, optimizing memory usage and program size. Both architectures influence modern processors, with RISC dominating mobile and embedded systems, while CISC remains prevalent in desktop and server applications.

Key Differences Between RISC and CISC

RISC (Reduced Instruction Set Computer) architectures utilize a small set of simple instructions optimized for high-speed execution and efficient pipelining, whereas CISC (Complex Instruction Set Computer) architectures contain a larger set of complex instructions aiming to reduce the total number of instructions per program. RISC processors typically have uniform instruction lengths and rely heavily on compiler efficiency, while CISC processors feature variable-length instructions with more addressing modes and built-in microcode. Performance differences stem from RISC's streamlined pipeline and simpler hardware, contrasted with CISC's ability to execute multi-step operations within single instructions, affecting power consumption and CPU design complexity.

Historical Evolution of Processor Architectures

RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) processors emerged from different historical needs in processor architecture development during the 1970s and 1980s. RISC architecture prioritized simple instructions executed rapidly, influenced by projects like IBM's 801 and Berkeley RISC, aiming for efficiency and pipeline optimization. Meanwhile, CISC evolved to handle complex instructions to reduce software complexity, exemplified by Intel's x86 architecture dominating early personal computing.

Instruction Set Complexity: RISC vs CISC

RISC (Reduced Instruction Set Computer) architectures feature a streamlined instruction set with fixed-length, simple instructions designed to execute within a single clock cycle, enhancing pipeline efficiency and minimizing decoding complexity. In contrast, CISC (Complex Instruction Set Computer) employs a diverse array of multi-cycle instructions with variable lengths, enabling complex operations but increasing decoding overhead and execution unpredictability. The simplified instruction set in RISC leads to better performance through faster instruction decode and execution phases, whereas CISC prioritizes versatility and code density by integrating complex addressing modes and microcoded control.

Performance Comparisons in Real-World Applications

RISC architectures often deliver superior performance in real-world applications by executing instructions at a faster rate due to their simplified design and reduced instruction cycles. CISC processors excel in complex tasks that benefit from fewer instructions and specialized operations, potentially enhancing performance in software with diverse instruction requirements. Benchmark tests in areas such as embedded systems and high-performance computing reveal that RISC architectures like ARM dominate energy efficiency and speed, while Intel's CISC processors maintain advantages in legacy software compatibility and versatile computing workloads.

Power Efficiency: RISC and CISC Perspectives

RISC architectures optimize power efficiency through simpler instructions that require fewer clock cycles per operation, reducing energy consumption in embedded and mobile devices. In contrast, CISC processors execute complex instructions with variable cycle counts, which can lead to higher power usage but improve performance for certain workloads. Power-conscious design in RISC chips often incorporates techniques like reduced instruction set pipelines and lower transistor counts, whereas CISC designs focus on integrating power-saving modes to balance efficiency and computational complexity.

Current Use Cases and Industry Adoption

RISC architectures dominate in mobile and embedded devices due to their power efficiency and simplified instruction sets, with ARM processors leading in smartphones and IoT applications. CISC processors, particularly Intel x86 series, remain prevalent in desktops, laptops, and servers because of their complex instruction sets that optimize legacy software performance. Industry adoption reflects these trends, with RISC architectures gaining traction in data centers for energy-efficient computing, while CISC maintains dominance in high-performance computing environments.

Challenges and Limitations of Each Architecture

RISC architectures face challenges with complex instruction sets that require multiple instructions to perform tasks, potentially increasing code size and memory usage. CISC designs encounter limitations in execution speed due to complex decoding stages and variable instruction lengths, leading to inefficient pipeline utilization. Both architectures struggle with balancing power consumption, with RISC focusing on simplicity and CISC on reducing code density, impacting overall system performance and efficiency.

Future Trends in Processor Design

RISC (Reduced Instruction Set Computer) architectures emphasize simplicity and efficiency with fewer instructions, enabling higher clock speeds and power efficiency crucial for future mobile and embedded systems. CISC (Complex Instruction Set Computer) designs continue evolving by integrating advanced instruction pipelines and sophisticated caching mechanisms to enhance performance in desktop and server environments. Emerging trends highlight the convergence of RISC and CISC features, driven by AI workloads and heterogeneous computing demands, optimizing both power efficiency and processing power.

Conclusion: Choosing the Right Architecture

Selecting between RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) architectures depends on specific application needs, power efficiency, and performance demands. RISC architectures offer streamlined instruction sets that enhance speed and energy efficiency, making them ideal for mobile and embedded systems. CISC architectures provide versatile and complex instructions suitable for desktop computing and legacy software support, ensuring compatibility and ease of programming.

RISC vs CISC Infographic

difterm.com

difterm.com